從零開始的 Xilinx SoC 開發(五)

這篇文章中,將會編譯出 bitstream,作為系列文前半部的收尾。為什麼可以說是收尾呢?因為在這篇結束之後,就會有好一段時間不需要打開 Vivado 了。(耶)

(複製貼上的)前情提要

在本系列的文章中,我們最終的目標是執行一個 Linux,上面可以使用到這些元件:

- CPU 側(又稱 PS side)

- CPU 本身

- DRAM

- FPGA 側(又稱 PL side)

- DRAM

- DMA,可以在兩個 DRAM 之間搬運資料。

之前的文章中,我們已經建立了 PS side 以及 PL side 所有必要的元件,並把他們之間相互連接,這篇中我們將會編譯出 bitstream,以利後續開發 Linux 上之驅動程式&軟體。

編譯 FPGA Bitstream

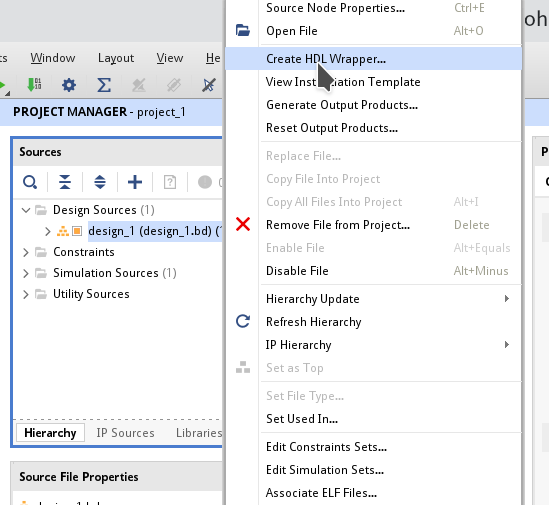

第一個步驟中,我們要把剛剛設計的 SoC 變成 Verilog 程式碼,為此,我們回到一開始的 project 頁面,點 Create HDL Wrapper。

接著在下方的 constraints 裡面新增一個 xdc 檔案,描述 Verilog 的每個 port 對應到的 FPGA 腳位,在這個 project 中,我們唯一有對外拉的 port 只有 PL 的 DRAM。關於 xdc 檔案裡面要怎麼寫,也是必須去找對應的 example 照抄最快,總之關於 FPGA IO 的部份抄 example 的就對了!

最後,有時候這個新加入的 sdc 並不會被自動啟用,用右鍵點一下 constraint 的資料夾,檢查一下確保有被啟用,這時 Make Active 應該是不能按的。

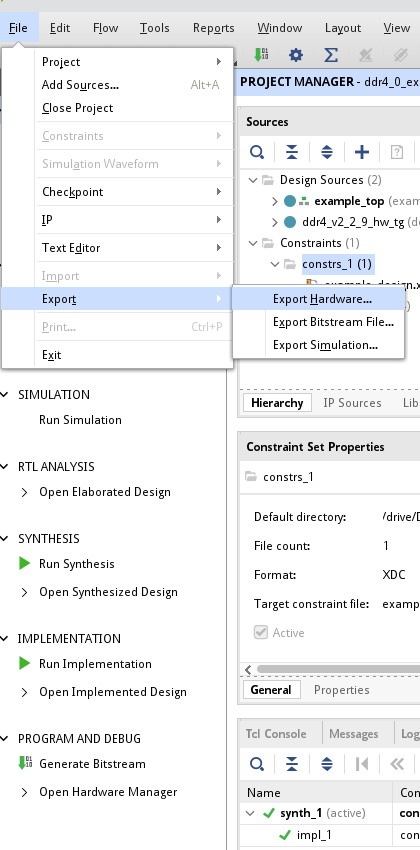

這時我們可以按下側邊欄的 Generate Bitstream 了(下圖下方),這步驟會花上一定時間,但是也沒什麼好說明的。

最後,這時我們可以 Export Hardware 了(下圖上方),這步驟會生成一個 xsa 檔案。我們選取 export 包含有 bistream 的選項,這樣 xsa 檔裡面便會包括了 SoC 的所有資訊以及編譯出來的 bitstream,對於我們要後續開發整個 Linux 系統是關鍵的檔案。

結論

到此,我們終於生成了一個 xsa 檔案,之後的 Linux 開發流程,將只需要這個檔案,而不需要 Vivado 了。接下來的流程中,將使用 PetaLinux,從 xsa 檔案產生出 Linux image、file system 等等資訊。

系列文連結

-

從零開始的 Xilinx SoC 開發(一)

-

從零開始的 Xilinx SoC 開發(二)

-

從零開始的 Xilinx SoC 開發(三)

-

從零開始的 Xilinx SoC 開發(四)

-

從零開始的 Xilinx SoC 開發(五)

- 從零開始的 Xilinx SoC 開發(一)

- 從零開始的 Xilinx SoC 開發(二)

- 從零開始的 Xilinx SoC 開發(三)

- 從零開始的 Xilinx SoC 開發(四)

- 從零開始的 Xilinx SoC 開發(五)